(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 6, June 2016

# A Novel Design of Low Power, High Speed VLSI for Processing Signals Using Multirate Techniques

S Vijaya Bhargavi<sup>1,</sup> K.Bhagya Lakshmi<sup>2</sup>

Asst. Prof, Department of ECE, Shadan Womens College of Engg & Tech, JNTUH, India<sup>1</sup>

Asst. Prof, Department of ECE, Shadan Womens College of Engg & Tech, JNTUH, India<sup>2</sup>

ABSTRACT: Multirate strategy is necessary intended for methods along with various enter along with productivity choosing premiums. The latest improvements with mobile computing along with transmission programs demand minimal energy along with excessive swiftness VLSI DSP methods [4]. That Cardstock offers Multirate quests employed for selection to provide transmission running with instant transmission technique. Several buildings designed for that design of minimal complexity, tad parallel Multiple Continual Multiplications function which in turn characterizes this complexity of DSP methods. On the other hand, main drawbacks of current strategies usually are often too costly or perhaps not necessarily efficient enough. In contrast, MCM along with digit-serial adder present option minimal complexity patterns, since digit-serial buildings enjoy a smaller amount area and therefore are independent of the data concept time-span [1][10]. Multiple Continual Multiplications is efficient solution to minimize how many inclusion along with subtraction with polyphase separate out implementation. That Multirate design methodology is methodical along with suitable to numerous complications. Within this report, awareness offers provided to this MCM & number serial buildings along with moving along with incorporating strategies that provides option minimal complexity with surgical procedures. That report likewise dedicated to Multirate Transmission Finalizing Modules applying Voltage along with Technological know-how climbing. Reduction of energy ingestion is significant intended for VLSI technique and in addition this will become essentially the most vital design parameter. Transistorized Multirate module which has whole custom made design along with various circuit topology along with optimization amount simulated with cadence platform. Multirate quests utilized AMI 0. 6 um, TSMC 0. thirty-five um, along with TSMC 0. twenty five um systems intended for various voltage climbing. The actual presented methodology gives a methodical solution to uncover circuit technique for excessive swiftness function in a minimal source voltage. Multirate polyphase interpolator along with decimator may also be developed along with optimized at new amount as a way to analyze this phrases energy ingestion, area along with swiftness.

**KEYWORDS**: VLSI-Very large scale integrated circuit, VHDL-Very high speed hardware description language, DSP-Digital Signal Processing, FIR: Finite impulse response, FPGA: Field Programmable gate array, MCM-Multiple Constant Multiplication

### I. INTRODUCTION

This Multirate techniques are integrated to lessen the computational complication. That Multirate design technique is actually thorough in addition to relevant to lot difficulties. There are several reasons to alter the trial price of any experienced facts indicate. Multirate filtration are interfaces involving constant & experienced facts that brings about a cost lessening parts together with development involving indicate excellent. Much of the investigation effort involving way back when a long time in the area involving electronic digital gadgets may be aimed towards growing the swiftness involving electronic digital systems. Just lately, the requirement involving portability and the modest development throughout battery power efficiency show that energy dissipation is probably the most essential design variables. This most critical variables for you to measure the caliber of some sort of routine are region, wait in addition to energy dissipation although challenging large swiftness. For this reason, throughout latest VLSI systems the ability

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 6, June 2016

wait product turns into probably the most crucial metric involving efficiency. This shown technique supplies a thorough method to obtain routine technique for large swiftness functioning in a lower provide voltage. It truly is normally acknowledged that lower energy circuits are really slower circuits in addition to large swiftness circuits expected very good energy use. In numerous practical application involving electronic digital indicate finalizing, there exists a difficulty involving altering the testing price of any indicate, both growing that or even minimizing that by simply some sum [2][5]. Telecommunication program transfers in addition to receives the various kinds of signals e. gary. fax, conversation, video etc. There exists a prerequisite for you to course of action different signals in the diverse costs with similar signals bandwidth. Digital camera sound executive can be an region which includes benefited significantly from Multirate techniques. One example is, it's found in the compact disc player to simplify the D/A conversion processes by maintaining the quality of the reproduced sound.

#### NEED OF MULTIRATE DSP:

A Discrete time system with unequal sampling rate at various part of the system is called Multirate system. Multirate digital signal processing is required in digital systems when more than one sampling rate is required. In digital audio, the various sampling rates used are 32 KHz for broadcasting, 44.1 KHz for compact disc and 48 KHz for audio tape. So, when audio professionals transfer recorded music to CDs, they need to do a rate conversion. Also, in digital video the sampling rate needed for composite video signals are 14.318 MHz for NTSC and 17.734 MHz for PAL. Both signals can be received in video receivers by sampling rate converter. But, the sampling rates for digital component of video signals are 13.5 MHz and 6.75 MHz for luminence and colour difference signal. Multirate signal processing is needed in digital transmission systems like teletype, facsimile and low bit rate speech where data is handled with different rates [2]. In speech processing, Multirate techniques are used to reduce the storage space or the transmission rate of speech data.

Basic Operations of Multirate DSP

Inside single price technique, only one testing price is used on top of a electronic indicate running programs while in Multirate technique the testing price is usually transformed at least once. It truly is popular pertaining to sound along with online video media running, verbal exchanges programs along with makes over examination. Various testing price can be purchased by using upsampler along with downsampler [3]. A good Upsampler increasing the price associated with recently tried indicate. As soon as In place testing is performed on series associated with types of a continuing perform or perhaps indicate then the item yields an approximation with the series which attained by testing the indicate from larger price. Any downsampler reducing the price associated with recently tried indicate. The basic functions in Multirate running for this purpose are generally Decimation along with Interpolation.

### MULTIRATE POLYPHASE FILTER STRUCTURE:

Polyphase is really a way of performing choosing price change that leads for you to quite successful implementations. Sample price reduction is essential pertaining to successful sign plus a choosing price increase is essential for your regeneration in the dialog. It may be efficiently applied employing limited impulse response digital camera filtration systems. It is located in which successful implementations involving reduced cross FIR filtration systems may be purchased by way of a means of minimizing the particular choosing price, filtering and increasing the particular choosing price towards first regularity [12]. FIR centered filtering is usually helpful in many digital camera indicate processing programs because of the prospects for exact linear phase and overall flexibility involving stability issues. Multirate process is employed within order involving high definition spectral investigation and also the design and implementation involving narrowband digital camera filtering.

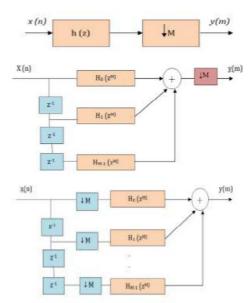

Polyphase Implementation of Decimator

The problem of designing Multirate Polyphase Interpolator & Decimator has received a great attention due to large number of multiplications. Decimator is utilized to decrease the sampling rate. The decimator consists of an antialiasing filter and a down sampler by a factor M depicted in Figure below,

(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 6, June 2016

Figure 1 Polyphase Representation of Decimator

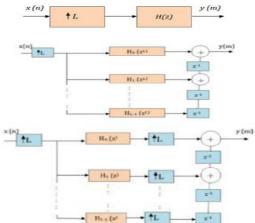

Polyphase implementation of interpolator focused that some of the delay line samples in an interpolator are zero valued. In this case the rate expander is removed to eliminate the need to store zero valued samples. In this approach, for each input samples fed into the delay line, the N/L delay line samples are used to compute L output samples with each samples computed with a different set of filter coefficient [13]. Telecommunication system transmits and receives the different types of signals. There is a requirement to process the various signals at the different rates with corresponding bandwidth. The role of a filter in decimation and interpolation is to suppress aliasing and to remove imaging.

Figure 2 Polyphase Representation of Interpolator

Digital Signal Processing has become essential to the design and implementation of high Performance audio, video, multi-media and communication systems. The efficiency of FIR filters for sampling rate conversion is improved using the Polyphase realization. Filtering is embedded in the interpolation process and polyphase structure is used to achieve the interpolation by a given factor at a low data rate.

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 6, June 2016

### **II. DESIGN METHODOLOGY**

### BASIC CONCEPT OF IMPROVEMENT

Your shown systems are actually split directly into about three periods wherein throughout very first phase, Transistorize Multirate module which includes top degree entire personalized pattern method can be developed along with voltage and technologies scaling. Within subsequent phase, region, electric power and speed productive processes for Multirate FIR filtration making use of MCM-digit serial architecture along with shifting-adding notion that offers substitute lower complication throughout surgical procedures and much better your boundaries can be shown. Within 3 rd phase, a competent procedure have been shown to help implement lower electric power, high speed Multirate Polyphase Interpolator & decimator which often suitable throughout wireless verbal exchanges methods. Strong kind, transpose kind and combined MCM-digit-serial adder can be proposed that offers lower complication types, sit on a lesser amount of region, lower electric power intake maintaining better speed.

### CMOS DYNAMIC LOGIC CIRCUIT TECHNIQUES:

Designing a CMOS dynamic circuit using a low supply voltage for the next generation CMOS VLSI is a challenge. CMOS dynamic logic circuit techniques have been used to enhance the speed performance of VLSI systems. The high speed design using Multirate approach increases the speed to a great extent but it increases the hardware complexity [10].

#### DESIGN OF TRANSISTORIZE MULTIRATE MODULE:

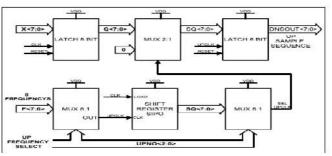

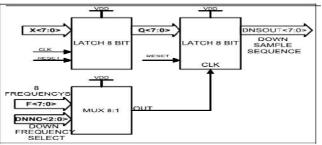

Transistorize Multirate module which has top level full custom design approach is developed with different circuit topology and optimization level. The new approach is used to reduce the complexity in the design to improve the essential parameters. The basic modules of Multirate signal processing are designed and verified its coefficients by the voltage and technology scaling. Upsampler consist of Shift register, D F/F and Multiplexer whereas downsampler consist of D F/F, clock generator and multiplexer.

Fig.3 Block Diagram representation of Upsampler

Fig. 4 Block Diag Representation of Downsampler

Scaling process has been done then it is simulated and synthesized on cadence platform. Obviously, some techniques applied to high speed circuits needed larger power consumption. However, it is directed that many techniques are used to reduced power dissipation in high speed circuits. Reduction of power consumption is important

(An ISO 3297: 2007 Certified Organization)

### Vol. 5, Issue 6, June 2016

for VLSI system and also it becomes one of the most critical design parameter. The basic Multirate modules are depicted as below,

### **III. EXPERIMENTAL RESULTS**

### PHASE-I: TRANSISTORIZE MODULE OF UPSAMPLER

The Transistorized module of Upsampler is designed using Multirate signal processing approach by Cadence software and analyzed the parameters on voltage & technology scaling. It is depicted in figure below, AMI 0.6  $\mu$ m, TSMC 0.35  $\mu$ m and TSMC 0.25  $\mu$ m technologies are used to improve the parameters.

Figure 5 Transisterize Circuit Diagram of Upsampler

Testing results are observed at various supply voltages which found satisfactory. The comparative analysis of the essential parameters at different technologies.

### TRANSISTORIZED MODULE OF DOWNSAMPLER:

Transistorized module of Downsampler is designed using Multirate signal processing approach by Cadence software and analyzed the parameters on voltage & technology scaling. AMI 0.6  $\mu$ m, TSMC 0.35  $\mu$ m and TSMC 0.25  $\mu$ m technologies are used to improve the parameters of Multirate modules.

Figure 6 Transisterize Circuit Diagram of Downsampler

### PHASE-II: MULTIRATE FIR FILTER DESIGN:

Multirate FIR filter is designed utilizing fresh strategies to improve parameters also to avoid signal intricacy. Multiplier, adders and latches tend to be diminished simply by unique common sense on account of that strength and region throughout process is actually diminished in fantastic prolong keeping better rate. Design and style answers are verified utilizing FPGA Cyclone–II Package. The interest has become fond of your MCM-digit serial architecture together with transferring & putting process that has option minimal intricacy throughout procedures and increased your parameters. The particular Attempts tend to be directed in the direction of reduction involving strength and region in fantastic prolong succeeded by using a number of continuous multiplier together with mix of digit-serial adder block. Inside introduced style continuous multiplier block utilizes shift-add techniques. Shift unit does not consume any area therefore total cell area is reduced. Similarly, the area of adder block is reduced by digit-serial architecture. Earlier design uses 32 full adders but this technique required only two adders. So, it is most efficient technique which reduced power consumption and area by large value maintaining higher speed.

(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 6, June 2016

Figure 7: RTL View of FIR Filter using MCM-Digit Serial Adder-shiftadds Concept

### **IV. CONCLUSION**

This kind of shown work is promoting structure technique as well as recent engineering notion to further improve the actual variables regarding Multirate DSP adventures. For you to wide open completely new possibilities of the actual Multirate adventures applying engineering as well as voltage running the important variables place, strength dissipation as well as rate has been discovered. New transistor technology have got preferred the ideal settings within Multirate DSP adventures. Prime levels method style method does apply that has granted entire personalized style together with various signal topology. AMI 0. 6 µm, TSMC 0. 30 µm as well as TSMC 0. 20 µm technology are employed for you to decided as well as improved upon the main variables regarding Multirate adventures. In the assessment effects, it really is discovered that will TSMC 0. 30 µm engineering at provide voltage required fewer strength dissipation retaining greater rate as well as TSMC 0. 20 µm engineering at 2V provide voltage retaining greater rates of speed at extremely fewer strength. This kind of Research methodology boosts some sort of rate as well as strength dissipation with the method. Next the Multirate FIR filtering was made within primary variety, transpose variety, applying MCM, applying MCM-digit serial structure and also the 6th method using mix off MCM-digit serial structure together with shiftingadding strategies to avoid signal complexity. Inside the paper, attention has been provided to the actual MCM-digit serial style together with shift-add approaches that include substitute reduced complexity within surgical procedures as well as improved upon the actual variables. The entire style the desired info is approved applying FPGA. In a very Last phase, component regarding Multirate polyphase Interpolator as well as Decimator provides presented with fresh designed method. These kind of adventures are created together with 4 various techniques which have been within primary variety, transpose variety, applying MCM as well as applying MCM-digit serial structure together with shiftadd strategies to avoid signal complexity. Progress in the variables will be purchased applying MCM as well as number serial adder way to an incredible magnitude as well as defeat issue regarding complexity & style effectiveness. Strong form of Multirate Polyphase Interpolator as well as decimator is most effective regarding setup regarding DSP method which usually demands extremely fewer strength dissipation retaining, higher speed. The complete results are verified using FPGA. Multiple Constant Multiplications is efficient way to reduce the number of addition and subtraction in polyphase filter implementation.

### REFERENCES

[1] L. Aksoy, E. Costa, P. Flores, and J. Monteiro, "Exact and approximate Algorithms for the optimization of area and delay in multiple constant Multiplications," IEEE Trans., Vol. 27, No. 6, pp. 1013–1026, Jun. 2008.

[2] An Yeu Wu, I. J. Ray, Liu Zhongying Zhang Kazuo Nakajima, R. M. Raghupathy "Low-Power Design Methodology for DSP system Using Multirate Approach" IEEE Transaction 1996.

[3] K. J. Ray Liu, An-Yeu Wu, Arun Raghupati, and Jie. Chen, "Algorithem based Low-Power and High-Performance Multimedia signal processing," Proceeding of the IEEE Vol.86 No.6, June 1998.

[4] An-Yeu Wu and K.J. Ray Liu "Algorithm Based Low Power Transform Coding Architectures: The Multirate approach" IEEE transaction on VLSI system Vol.6 No.4, Dec.1998.

[5] H.Nguyen and A. Chatterjee, "Number-splitting with shiftand- add Decomposition for power and hardware optimization in linear DSP Synthesis," IEEE Trans. VLSI Syst., Vol.8, No.4, pp.419–424, Aug. 2000.

[6] Mandeep Singh Saini and Rajivkumar, "Optimal design RRC Pulse Shape Polyphase FIR decimation filter for Multistandard wireless" (IJARCET) Volume 1, Issue 10, December 2012, Finland.

[7] L. Aksoy, E. Gunes, and P. Flores, "Search algorithms for the Multiple Constant Multiplications problem: Exact and approximate" J. Microprocess. Micropyst. Vol. 34, No. 5, pp. 151–162, Aug. 2010.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 6, June 2016

[8] Mustafa Aktan, Arda Yurdakul, and Gunhan Dundar, "An Algorithm for the Design of Low-Power Hardware-Efficient FIR Filters" IEEE Transactions on Circuits and Systems-I, Vol. 55,

6, July 2008. [9] M. Thenmozhi, N. Kirthika "Analysis of Efficient Architectures for FIR Filters using Common Sub-expression Elimination

6, July 2008. [9] M. Thenmozhi, N. Kirthika "Analysis of Efficient Architectures for FIR Filters using Common Sub-expression Elimination Algorithm" International Journal of Scientific & Technology Research Volume 1, Issue 4, May 2012.

[10] Levent Aksoy and Cristiano Lazzari, Paulo Flores and Jose Monteiro, "Optimization of Area in Digit-Serial Multiple Constant Multiplications at Gate-Level" IEEE Transaction, 2011.

### BIOGRAPHY

S Vijaya Bhargavi<sup>1,</sup> M.Tech, Assistant Professor, Dept of ECE, Shadan Womens College Of Engg & Technology. She had completed hes M.Tech, and Area of Interest in Communication Systems. Her presented and published in various national and international conferences and journals.

**K.Bhagya Lakshmi**<sup>2,</sup> M.Tech, Assistant Professor, Dept of ECE, Shadan Womens College Of Engg & Technology. She had completed hes M.Tech, and Area of Interest in Communication Systems &Design of Systems. Her presented and published in various national and international conferences and journals.